Layout design

The custom layout design platform that realizes both high quality and shortening design time by reusing the craftsmanship and automating layout design that coordinates designers and automatic tools.

■Features

- Uses a variety of design techniques, to achieve a degree of freedom and scalable design environment.

- Support large scale data (Stream 100 GB scale, 10 million net scale)

- Cooperates with polygon editing and net driven editing

– Enable rule-driven editing with automatic electrical potential recognition and net tracking funct - Template based constraint driven layout

– Improve design quality using templates such as Pair group layout - generation

- Shorten the design period with a variety of optional tools specialized for a design target

- Analysis and learning function

– Follow the work procedure of the designer with craftsmanship, shorten the design period with the optimum procedure

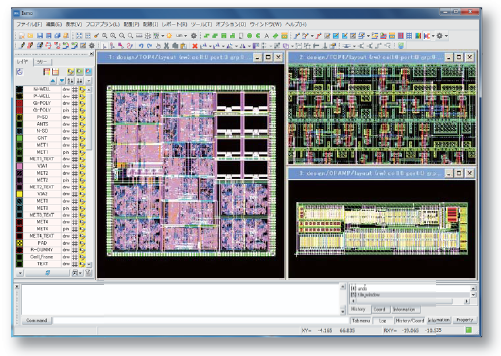

Layout Design System

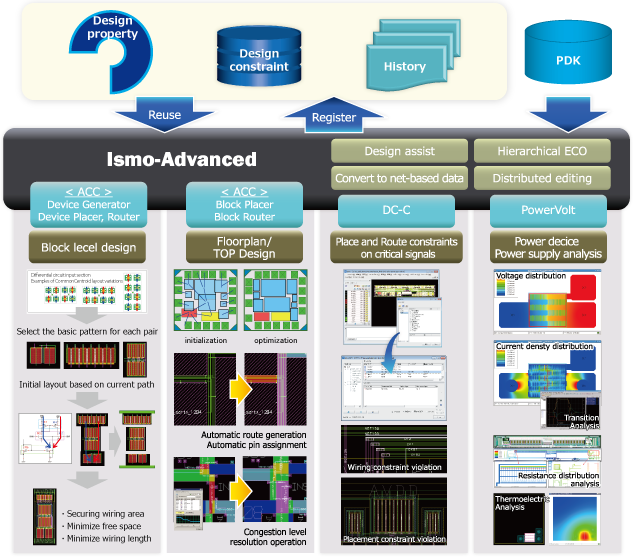

SX-Meister Ismo-Advanced

Realizes a highly flexible and scalable design environment with a wide variety of design methods

Support for large scale data (Stream 100 Gbyte scale, 10 million net scale or more)

Shorten TAT by using a wide range of optional tools specialized for the design target

Integration of polygon editing and net-driven editing

- Automatic potential recognition of polygon shapes and net tracking enablerule driven editing.

- Push Aside function for wiring and automatic loop elimination function

- Automatic net construction function when wiring is input

Constraint-driven editing

- Layout editing function that preserves circuit constraints

High operability

- Multi-language menu (Japanese mode, English mode)

- Windows-like operability

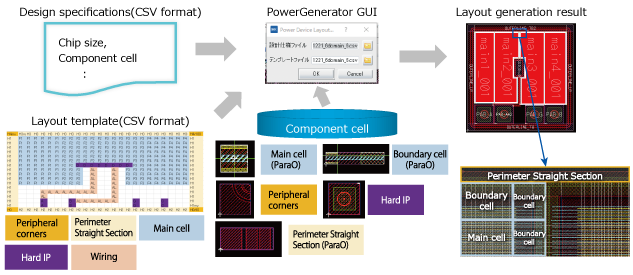

Automatic Power Device Layout Generator

SX-Meister PowerGenerator

Automatic chip layout generation for power devices (IGBT/RC-IGBT/SiC).

Reduces design man-hours by automatically generating power device layouts from simple floorplan information without requiring complex rules and settings.

- Automatic generation of layout (placement and wiring) from design specifications and templates described by CSV.

- Calculate device size from chip size and template, and place main cells in array.

- Automatic cell placement on chip periphery area.

- Automatic cell placement dedicated to the main cell boundary.

- Supports modification and reallocation of main cell placement area after layout generation.

Download

Download