|

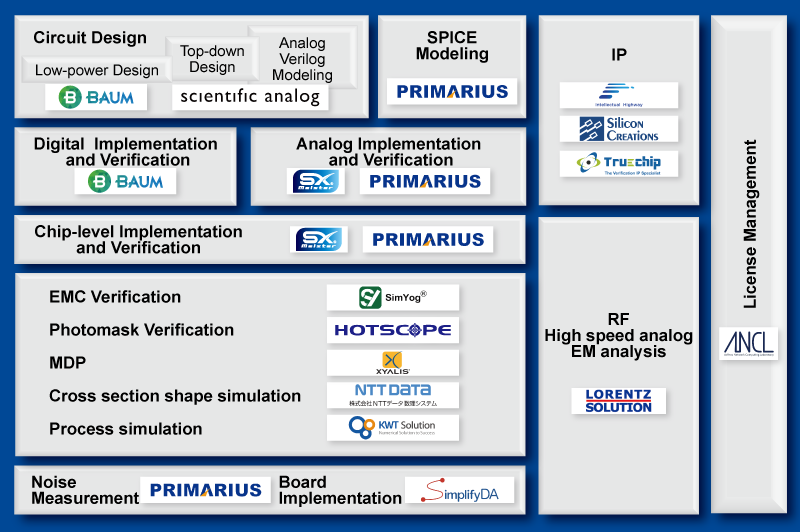

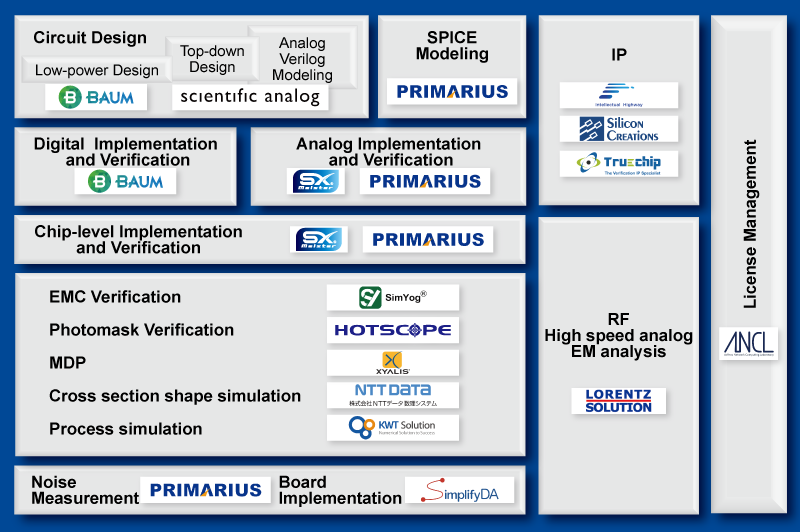

License Management

|

|

HPC environment integrated operation middleware ShareTask

|

|

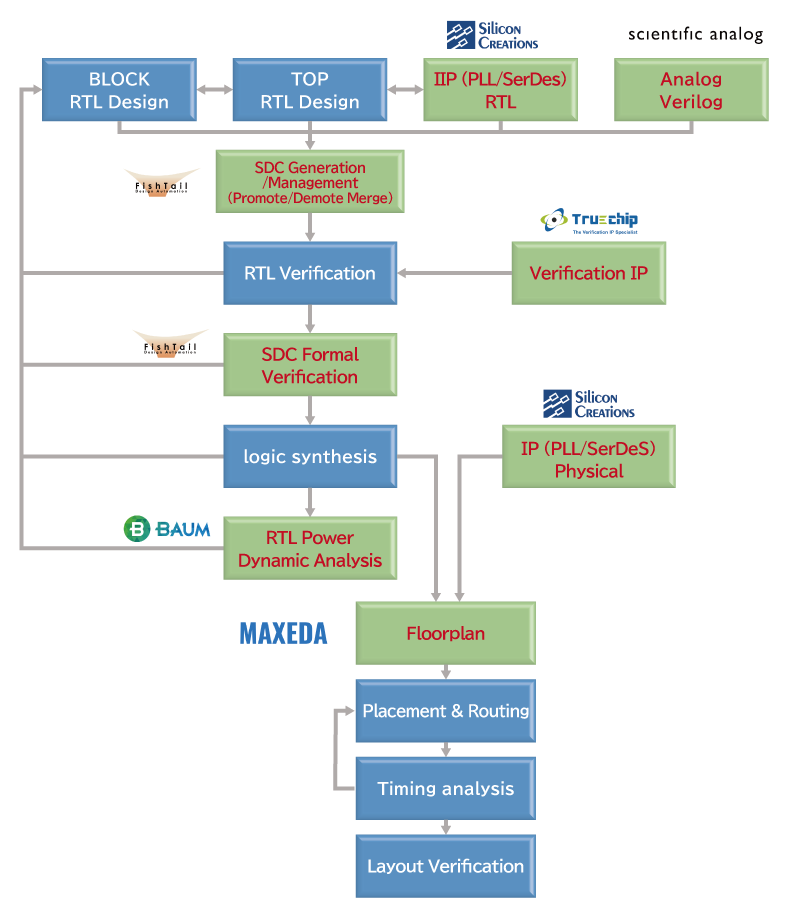

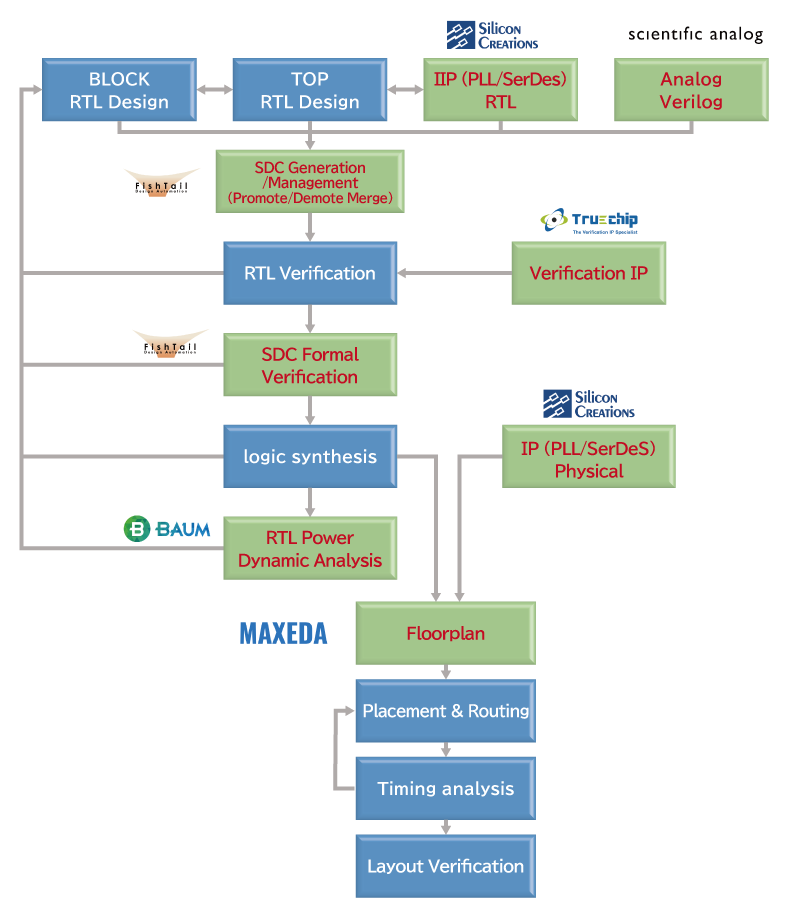

RTL Design

Digital Implementation and Verification

Analog Implementation and Verification

|

|

Generate high quality SystemVerilog models from analog circuits and verify

|

|

RTL Design

Low-power Design

|

|

RTL high accuracy and high speed power consumption analysis

|

|

SPICE Modeling

Analog ,Chip-level Verification

Noise Measurement

|

|

SPICE Simulator, Modelling tool, Noise measurement

|

|

Analog Implementation and Verification

|

|

Integrated Circuit design and layout design system

|

|

IP

|

|

The most-advanced process IP: PLL/SerDes/LVDS-IO

|

|

IP

|

|

Verification IP Tool set (USB~AMBA over80)

|

|

IP

|

|

PTU ( Protocol Termination Unit )

|

|

EM analysis

|

|

EM analysis platform IC・Package・PCB

|

|

Mask Data Preparation (MDP)

|

|

MDP tool set

|

|

Cross section shape simulation

|

|

Cross section shape simulation

|

|

Process simulation

|

|

Plasma etching simulation

|

|

Board Implementation

|

|

High wiring rate topology-based auto routing

|

|

EMC Verification

|

|

EMC Virtual Laboratory (RE/CE/RI/CI)

|

|

Photomask Verification

|

|

Analysis browser for DFM/Photomask verification

|