Layout Verification

Design Constraint Driven Layout Verification

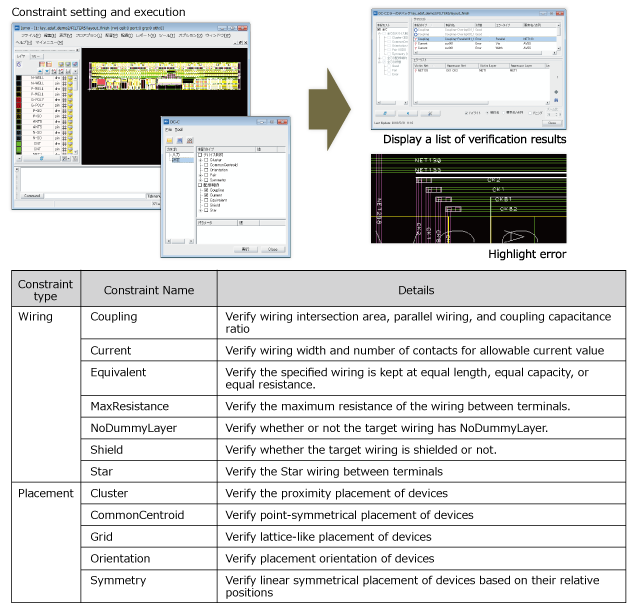

SX-Meister DC-C

Improves design quality by reducing errors early in the layout process

Reduce rework and significantly shorten design time by preventing violations of design constraints.

- It is possible to verify different design constraints for each instance and net,

- which cannot be fully verified by DRC, LVS, or LPE, from the early stage of layout.

- Ease of schematic-based constraint setting

- Easy creation and editing of constraint rules using GUI

- Display information needed to verify failure locations

- Graphic color guidance display

SX-Meister Mentor Calibre I/F

Calibre execution from Ismo-Advanced and debugging by RVE

- Shorten verification time by seamlessly incorporating the Calibre verification process into the SX-Meister custom automated design flow.

- Directly launch Calibre during design to verify layout.

- View and debug verification results directly.

Download

Download