JEDAT社およびパートナー企業の DAC2018 出展情報について

株式会社ジーダット

イベント情報

お客様各位

2018年5月22日

株式会社ジーダット

JEDAT社およびパートナー企業の DAC2018 出展情報について

来る2018年6月25日から27日まで、米国カルフォルニア州サンフランシスコにて開催されます「55回 DAC(Design Automation Conference)」において、当社および、パートナー各社は、下記の通り展示・デモを行います。

DACにお越しの際は、是非各社ブースにお立ち寄りくださいますようお願い申し上げます。

デモのご予約は下記メールにて受け付けておりますので、お手数ですが事前連絡をお願いいたします。

ご予約、お問い合わせは こちら

Jedat Inc. Booth: #2339

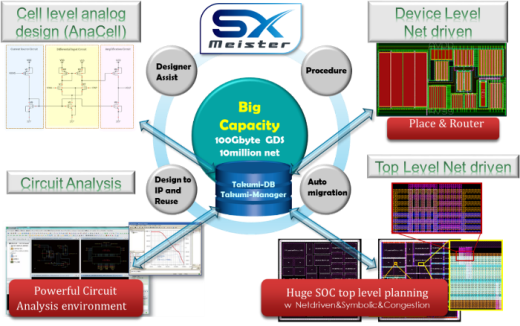

■ SX-Meister:

LSI設計者の匠の技を反映・継承して、高品質な設計を実現できる次世代回路・レイアウトシステム

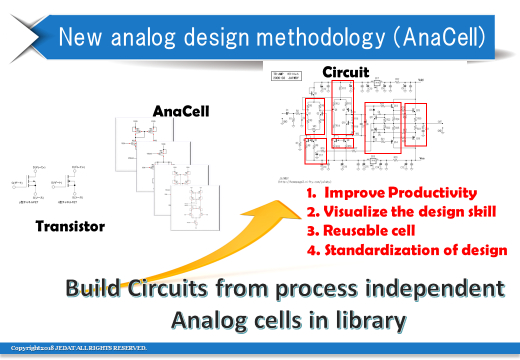

■ SX-Meister/Asca-Advanced

要素回路単位のセル(AnaCell)を用いた、アナログ設計を可能とし、設計効率の向上、設計資産の蓄積の標準化を可能とします。新たに開発した自動バイアス設定機能によりさらに効率化が可能となります。

■ SX-Meister/GT-Router

大規模カスタムSoCや、アナログチップでのクリティカルな信号・電源線を制約ドリブンで自動配線を可能とします。

Dorado Design Automation, Inc. Booth: #2417

■ Intel, Samsung,および TSMCの全ての先端7nmのECO フローが整う

■ 新たなECO Platformとして、Recovery system (Area/Power/Reliability)が統合される

■ 新たなECO Platformで、dynamic power ECO, IR drop ECOをサポート

■ 4つの実用的なECOフローがすべてのニーズをカバー :

- Hierarchical ECO Flow : Fast timing closure for huge hierarchical chips.

- Tweaker Low Power Flow : Minimum over design for low power chips.

- Advanced ECO Flow : Effective timing fix for critical timing paths.

- Tweaker CPU Flow : Balanced power & chip for CPU cores.

FishTail Design Automation, Inc. Booth: #2648

制約検証、生成、管理のソリューションを紹介します。

■ 制約検証

- フォーマルな検証、Generated ClockのPeriod/Alignment、Timing exception、非同期リセット、グリッチ、reset domain crossing検証

- 検証とアサーションフローにより、1-3%までエラーを自動で削減し、デバグを可能とします。

■ 制約生成

- RTLからClock 定義/Clock groupsを自動抽出し、EXCELやclockブラウザーで管理できます。

- タイミングに影響なしにclocks/registerを削減します。例えば、1つのSDCファイルに多くのfunctionalかtest modeの制約がある場合、P&Rの実行速度を2倍向上させることが可能です。

- フォールスパス・マルチサイクル・clock groupsなどのtiming exceptionを生成し、QoRを向上

■ 制約管理

- 制約のトップ階層、ブロック階層間で制約情報のマッピングをおこない、その間で等価性検証を行うことで、ピンポイントでデバッグを行うことが可能性になります。

Fractal Technologies Booth: #2333

最先端のIP検証ツール

■ 設計で使用されるあらゆるデータフォーマットに対して、それらの一貫性をチェックし検証します。これによりスタンダード・セル・ライブラリ、IOライブラリ、汎用IPブロック(デジタル、ミックスド・シグナル、アナログおよびメモリ)の品質を向上させることができます。

■ Crossfireソフトウェアに加え検証サービスやカスタマイズサービスを提供しています。

IC Manage, Inc. Booth: #2618

■ GDP XL:

Plastic SCMベースの分散データ管理に対応した新しいHybridデータ管理ツール

■ PeerCache:

オンプレミスのディスク統合環境

■ PeerCache Cloud:

クラウド環境を含めた統合設計環境

■ Envision:

設計見える化ツール

ProPlus Design Solutions, Inc. Booth: #2439

■ NanoSpice Giga(TM) が実現する、FastSPICEに代わる高精度ソリューション

- メモリ・フルチップ設計を可能にする、10兆個の素子を扱う唯一の SPICE シミュレータ

- 電流・パワー・タイミングを正確にシミュレーション可能

- マルチスレッドによる速度スケーラビリティ

- FastSPICE 特有のシミュレーションオプション不要

■ NanoSpice(TM) が実現する、既存 SPICE に代わる高スループットソリューション

- アナログ・ミックストシグナル設計を余裕でこなす、5,000万個以上の素子を扱う最高速のSPICE シミュレータ

- 既存 SPICE シミュレータとの互換性を完全に維持しつつ、経済的なスケーラビリティを提供するパラレルSPICEシミュレータ

■ プロセスとデバイスをよりよく知ることで、競争力を強化するソリューション群

- ファウンドリの標準モデリングツール BSIMProPlus(TM)- 1/f雑音測定とプロセスばらつきを測定する,業界標準システム 9812DX

- プロセスとデバイスを評価・解析して回路設計をアシストする ME-Pro(TM)

- 回路のプロセスばらつき特性を評価、予測し、PPA(Power/Performance/Area)と歩留まりの向上に寄与するNanoYield(TM)

Scientific Analog, Inc. Booth: #1357

■ XMODEL

Analog/Mixed Signal System を、機能モデルまたは回路レベルモデルを用いて、SystemVerilogシミュレータ上で高速・高精度シミュレーションすることを可能にします。XMODEL は、SPICE を起動することなく SystemVerilog 上でアナログ回路をシミュレーションすることができるため、SPICE・Verilog-AMS・Real-Number Verilog など、既存のツールでは困難なディジタル・アナログ混載の大規模Mixed Signal システムの検証を容易にします。

■ GLISTER

Cadence(R) Virtuoso(R) 環境に組み込む,XMODEL と MODELZEN 向けの GUI です。GLISTER を用いることで、コードを書くことなく回路図上で簡単にアナログ回路の SystemVerilog モデルを構成し、XMODEL シミュレーションが実行できます。

■ MODELZEN

XMODEL プリミティブを用いて、回路ネットリストから SystemVerilog モデルに変換する、アナログ回路用自動モデル生成ツールです。

皆様のご来場をお待ち申し上げております。

お問い合わせ、ご予約は こちらまでお願いいたします。

以上

2018年5月22日 第1報

2018年5月24日 Fractal Technologies、IC Manage, Inc.、ProPlus Design Solutions, Inc.の出展情報を追加しました

*パートナー企業の情報は随時追加いたします。

Download

Download