ACC(Analog Chip Compiler)BlockPlacer/BlockRouterリリースのお知らせ

株式会社ジーダット

NEWS

ACC(Analog Chip Compiler)BlockPlacer/BlockRouterリリースのお知らせ

株式会社ジーダット(本社:東京都中央区、社長:松尾和利、以下「ジーダット」)は、SX-Meister ACC(Analog Chip Compiler)シリーズのうちチップレベル設計環境として、ブロック配置ツールBlockPlacer、自動配線ツールBlockRouterの2製品をリリース致します。

ACC(Analog Chip Compiler)とは、ジーダットが開発した、アナログIC全体の機能、性能を実現するためのパターン設計を自動化する製品群の総称です。従来は手動の設計によって行っていた、アナログIC全体のパターン設計を自動化することで、アナログICに関する設計経験が浅い設計者でも、設計制約を守った高品質なパターン設計を短時間で生成できるようになるため、数少ないベテランのアナログ設計者に頼ることなく、高品質なアナログチップが短納期で提供できるようになります。

■ BlockPlacerの紹介

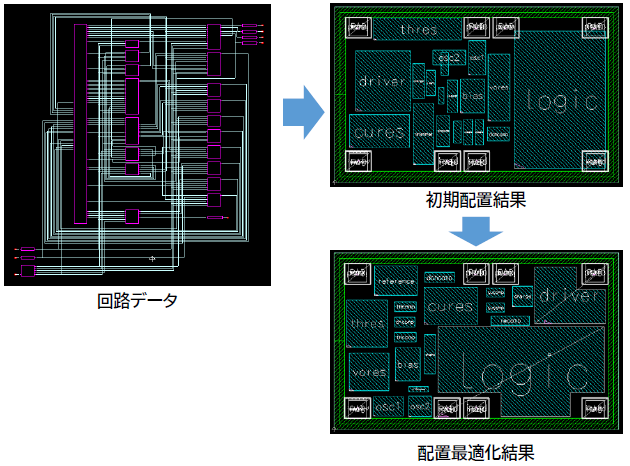

BlockPlacerはチップレベルのブロック配置ツールです。フロアプランの初期段階において、ネットリスト・配置領域・PAD(及び外部ポート)の配置座標を事前に設定してレイアウトデータの入力とし、下記内容を実現するブロック配置を自動で行うことができます。

【BlockPlacerの特徴】

- 最適なプロアプランを早期に決定可能な自動配置機能

- 初期配置:ネット優先度 (重み付け)を考慮し、総配線長が最小になる初期配置

- 配置最適化:初期配置結果を大きく変えず、総配線長を短く保ちながら、空き領域が最小となるよう、重なり除去・ブロックの移動及び回転・ソフトブロック形状を変形(Aspect比, 多角形化)

- 配置制約:整列・対称性・間隔を考慮

■ BlockRouterの紹介

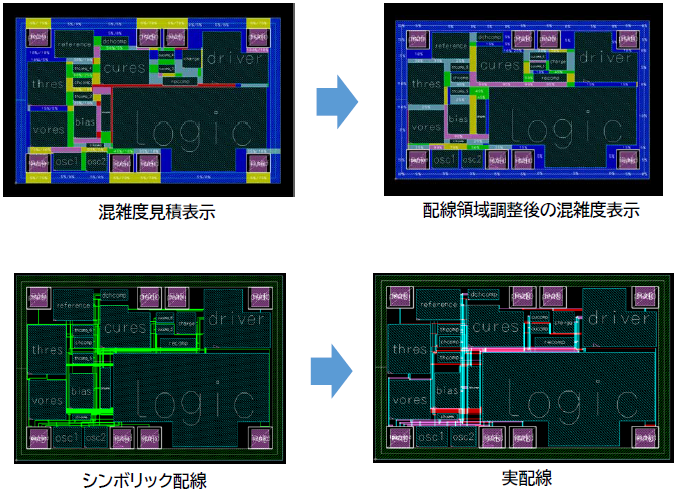

BlockRouterはチップレベルのブロック間自動配線ツールです。制約や配線混雑度に応じて経路を自動調整し、デザインルールを守った高精度、高密度の配線を実現します。BlockPlacerで作成したフロアプランに対し、実際に配線を行うことで必要な配線領域をフィードバックしてフロアプランを早期にフィックスすることで、従来のマニュアル設計と比較し、設計期間を短縮できます。

また、BlockRouterはシンボリック配線をベースに動作するため、配線結果に対するマニュアル修正も容易に実施可能です。編集機能により経路を変更後、レイヤと幅を自動調整し、最終経路とすることができます。

【BlockRouterの特徴】

- 配線制約に応じて配線領域や形状を自動決定する制約ドリブンルータ

- ソフトブロック端子生成:配線引き込み位置にソフトブロックのポートを自動生成

- 概略経路割当:配線対象ネットに対し配線経路・レイヤ・幅を自動決定。配線領域見積もりのための最短配線と配線領域確定後の配線混雑度考慮を選択可能

- 混雑度見積もり:概略経路割当の結果から配線混雑度をエディタ上に視覚的に表示、ブロックの移動や変形による配線領域の配分調整を容易化

- 詳細経路割当:配線の並び順や配線間隔を調整、必要に応じジョグ挿入を含め、配線経路を確定

- 陣取り/実体化:シンボリック配線からシールドやメッシュ状のスリット配線を含め最終の実配線を作成

■ 株式会社ジーダット(Jedat Inc.)概要

所在地:東京都中央区湊1-1-12 HSB 鐵砲洲

創 業:2004年2月2日

資本金:760,982,760円

代表者:代表取締役社長 執行役員 松尾 和利

URL:https://www.newjedat.arum-net.com

事業内容:半導体やFPD(Flat Panel Display)向けCADソフトウェア(EDA)の研究、開発、販売およびコンサルテーション

■ 本件に関するお問い合わせ先

○ 株式会社ジーダット

営業本部 営業企画部 小野 信任

TEL:03-6262-8401

E-mail : こちらをクリック

Download

Download