株式会社ジーダット

制約ドリブン自動配置配線システム

ACC Analog Chip Compiler

ACC Analog Chip Compiler

アナログICの設計制約を遵守する⾃動設計環境

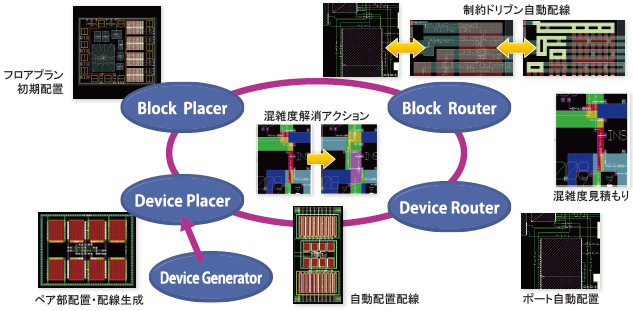

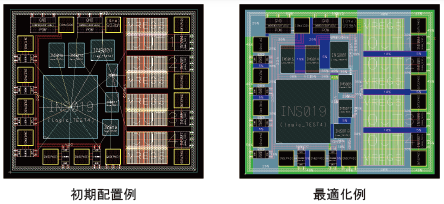

チップレベル、ブロックレベルの設計制約を考慮し、設計者の考え⽅に従った手順でレイアウト自動化を実現

■ACCの主な特長

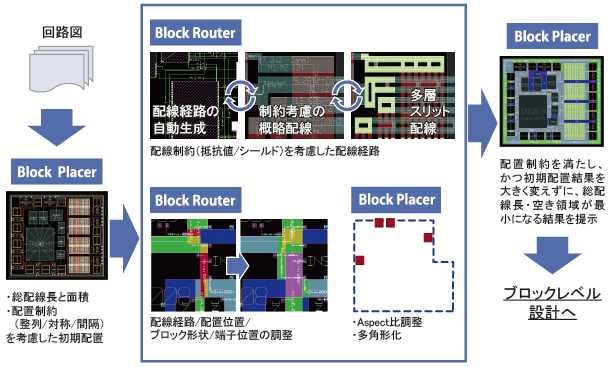

チップレベル設計

- 最適なフロアプランを早期に決定可能な自動配置機能

- 配線制約に応じて配線領域や形状を自動決定する制約ドリブンルータ

- 最寄りの配線引き込み位置にソフトブロックのポートを自動配置

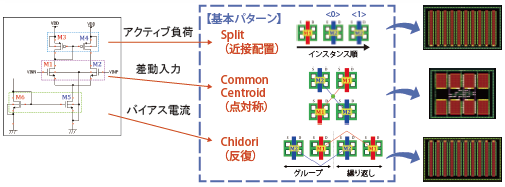

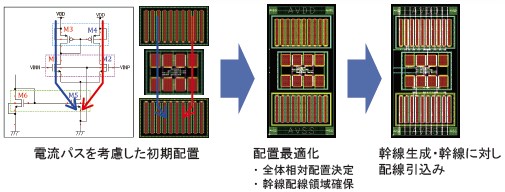

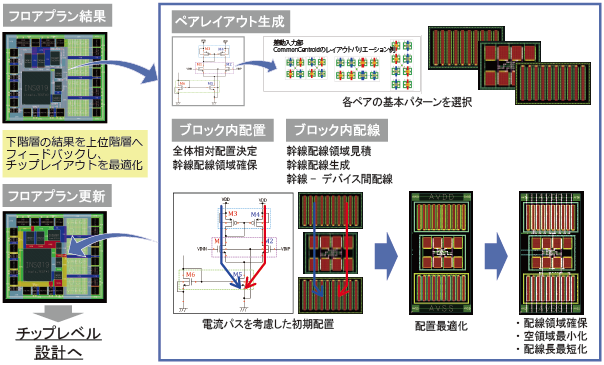

ブロックレベル設計

- 基本パターンを用いて、ペアの配置/配線を容易かつ高品質に生成

- 電流パスやデバイス種別などを考慮した初期配置と、その初期配置に対して適切な配線領域を確保する配置最適化機能

- 手修正を極力必要としない配線生成方式を採用した自動配線機能

■Block Placer

特長

- ネット優先度 (重み付け)を考慮し、総配線長が最小になる初期配置

- 初期配置結果を大きく変えず、総配線長を短く保ちながら、空き領域が最小とな るよう、重なり除去、ブロックの移動・回転、ソフトブロック形状を変形(Aspect比, 多角形化)

- 配置制約 (整列配置・対称配置・間隔配置) を考慮

■Block Router

特長

- 配線制約(抵抗値・シールド・インピーダンス分離・最大幅)を満たし、配線経路・レイヤ・幅を自動決定

- 配線引き込み位置にソフトブロックのポートを自動生成

- 自動経路入力の結果から配線混雑度をエディタ上に表示

- 高混雑度配線領域の混雑度緩和に有効なアクション(ブロックの移動・変形)と予測効果を提示し、インタラクティブ又はバッチでアクションを実行

■Device Generator

特長

- 基本パターンを用いて、ペアの配置/配線を高品質に生成

- 基本パターン(Common Centroid・たすき・CrossCouple… etc)をベースとしたバリエーション生成(基本配置パターンの自動展開)、サイドダミーの追加

- レイアウト生成時に、デバイス間の配線パターンやMPLガードリングを生成

■Device Placer / Device Router

特長

- 電流パス順及びデバイス種別毎の塊(クラスタ)を考慮した上で配線長・面積(配置領域・配線領域)が適切となる配置を取得

- Device Placerで認識した電流パス及び配置結果を用いて、重要ネットを優先した幹線生成・幹線に対する配線引き込みを行うことで、不要な迂回や折れ曲がりの無い配線を生成

■ACCが提案するチップレベル設計フロー

■ACCが提案するブロックレベル設計フロー

■サポートプラットフォーム

Windows/Linux

※詳細はこちらのソフトウェアサポートOS一覧をご参照下さい。

Download

Download