株式会社ジーダット

SDC検証

Fishtail Confirm-SDC Verification

Fishtail Confirm-SDC Verification

タイミング例外検証・生成・管理ツール

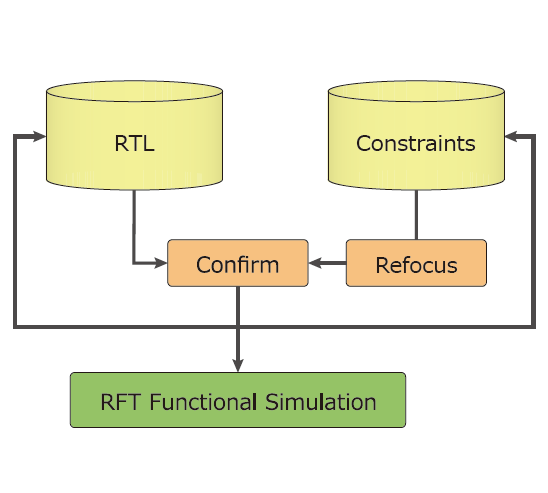

FishTailのSDC検証フローは、GateまたはRTLレベルのTcl制約とともに、設計データのRTL記述を読み取ります。 Refocusは、制約を設計データにマップし、構文と制約の問題をチェックします。制約はConfirmを使用してFormalに検証され、強力なデバッグ環境を使用して設計者に提示されます。Formalな検証にFailした制約は、Confirmによって生成されたアサーションに変換され、RTLシミュレーションに統合されます。

シミュレーション結果は内部で統合され、Failした制約のデバッグが容易になります。確認は、SDCのFormalなLintを実行し、誤ったマルチサイクルパス、生成されたクロック波形、および生成されたクロック間の整合性を検証します。さらに、Confirmを使用して、設計データがグリッチから安全であることを確認し、CDC / RDC検証を実行します。

FishTail Design Automationは、オレゴン州ポートランドとインドのバンガロールを拠点として2002年に設立されました。

■Gate-Levelシミュレーションを不要に

当社のSDC検証ソリューションは、誤った制約に起因するシリコンの障害を回避します。これにより、Gate-Levelのシミュレーションが不要になります。

Gate-Levelのシミュレーションは制約のバグを検出するためには、不完全で、しかも往々にして1日で終わりません。

■No Noise

制約検証用に特別に開発された独自のFormalなエンジンを使用することにより、設計者にノイズ(不用なWarningや、疑似エラーなど)が多発することはありません。微妙な問題については、制約の正確さのために、進んだ検証手法によってコメントを付与します。

■RTLシミュレーションによるシームレスな統合

Formalに証明できないものは、SystemVerilogアサーションに変換されます。Confrimによって生成されたSVAはRTLシミュレーション環境に統合され、既存のリグレッションテストを再利用しながら制約の正確さを確立します。

ConfirmはRTLをゲートに変換しないため、RTLシミュレータとの統合はシームレスです。Confirmによって生成されるSVAはコンパクトで、設計データ上の任意のRTLを参照できるため、ロジックコーンの複雑さの影響を受けません。

ReForcusを使用すると、GateLevelの制約をRTLにマッピングして、RTLを使用したSDCサインオフを可能にします。

■レビュー容易性

FishTailのFormal+ABV SDC検証メソドロジーにより、設計者は実際の制約の問題を確認できます。FishTailのSDC検証ソリューションを使用する際に必要なレビュー作業が少ないため、組織内で広く展開できます。

■適用内容

Formal SDC Lint

Generated Clock Waveform Verification

Timing-Exception Verification

Glitch Verification

Clock-Domain Crossing Varication

Reset Domain Crossing Verification

Download

Download